Una tabla de verdad, o tabla de valores de verdad, es una tabla que despliega el valor de verdad de una proposición compuesta, para cada combinación de valores de verdad que se pueda asignar a sus componentes.1Fue desarrollada por Charles Sanders Peirce por los años 1880, pero el formato más popular es el que introdujo Ludwig Wittgenstein en suTractatus logico-philosophicus, publicado en 1921

Compuertas lógicas:

Una compuerta lógica es un circuito lógico cuya operación puede ser definida por una función del álgebra lógica, cuya explicación no es el objeto de esta obra.

Veamos entonces las compuertas lógicas básicas, para ello definamos el termino “tabla de la verdad”, por utilizarse a menudo en las técnicas digitales.

Se llama tabla de verdad de una función lógica a una representación de la misma donde se indica el estado lógico “1” o “0” que toma la función lógica para cada una de las combinaciones de las variables de las cuales depende

compuerta lógica NAND:

La función NO-Y, llamada mas comúnmente NAND es la negación de la función Y (AND) precedente. Así como en una puerta Y se necesita que exista nivel 1 en todas las entradas para obtener el mismo nivel en la salida, en una NAND el nivel de la salida seria 0 en las mismas condiciones. Por el contrario, cuando hay un nivel 0 en alguna de las entradas de una puerta Y la salida esta a nivel 0, mientras que en iguales circunstancias en una puerta NAND el nivel de salida seria 1. Una designación más adecuada habría sido AND invertido puesto que Es la función AND la que se ha invertidoCompuerta lógica NOR :

La función NOR consiste en la negación de la O, o sea, asi como esta suministra nivel 1 a su salida si cualquiera de las entradas que posee esta a nivel 1, una puerta NOR se comporta justamente al revés. En la función NOR es suficiente aplicarle una cualquiera de sus entradas para que niegue su salida. la NOR pueden tener más de dos entradas, y la salida es siempre el complemento de las funciones AND u OR, respectivamente.

Puerta NO-Y (NAND)

La puerta lógica NO-Y, más conocida por su nombre en inglés NAND, realiza la operación de producto lógico negado. En la figura de la derecha pueden observarse sus símbolos en electrónica.

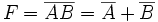

La ecuación característica que describe el comportamiento de la puerta NAND es:

Su tabla de verdad es la siguiente:

| Entrada A | Entrada B | Salida  |

|---|---|---|

Podemos definir la puerta NO-Y como aquella que proporciona a su salida un 0 lógico únicamente cuando todas sus entradas están a 1.

[editar]Puerta NO-O (NOR)

La puerta lógica NO-O, más conocida por su nombre en inglés NOR, realiza la operación de suma lógica negada. En la figura de la derecha pueden observarse sus símbolos en electrónica.

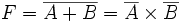

La ecuación característica que describe el comportamiento de la puerta NOR es:

Su tabla de verdad es la siguiente:

| Entrada A | Entrada B | Salida  |

|---|---|---|

Podemos definir la puerta NO-O como aquella que proporciona a su salida un 1 lógico sólo cuando todas sus entradas están a 0. La puerta lógica NOR constituye un conjunto completo de operadores.

Puerta OR

La puerta lógica O, más conocida por su nombre en inglés OR ( ), realiza la operación de suma lógica.

), realiza la operación de suma lógica.

), realiza la operación de suma lógica.

), realiza la operación de suma lógica.La ecuación característica que describe el comportamiento de la puerta OR es:

Su tabla de verdad es la siguiente:

| Entrada A | Entrada B | Salida  |

|---|---|---|

Podemos definir la puerta O como aquella que proporciona a su salida un 1 lógico si al menos una de sus entradas está a 1.

compuerta xor

La OR - exclusiva se denomina la puerta de << algunos pero no todos >>. El termino OR - exclusiva con frecuencia se sustituye por XOR. La tabla de verdad para la función XOR se muestra en la tabla 10 . un cuidadoso examen muestra que esta tabla de verdad es similar a la tabla de verdad OR, excepto que cuando ambas entradas son 1 la puerta XOR genera un 0. | XOR | |||

0 1 1 | 1 0 1 | 1 1 1 | 1 1 0 |

La operación de una puerta XOR es análoga a la del circuito eléctrico mostrado en la fig. 18. los interruptores A y B simulan las entradas y la lampara (Y) la salida .

Los interruptores A y B están acoplados mecánicamente a los interruptores A y B de modo que cuando A se cierra entonces A se abre y viceversa . lo mismo puede decirse del interruptor B con respecto al B.

Cuando los interruptores A y B están ambos cerrados o ambos abiertos la lampara no enciende. En cambio , cuando uno de ellos , por ejemplo el A , esta abierto y el otro, B, esta cerrado , entonces la lampara se enciende.

Una booleana para la puerta XOR puede obtenerse de la tabla de verdad la fig. 19 la expresión es A ·B + Å · B = Y a partir de esta expresión booleana puede construirse un circuito lógico utilizando puertas AND, puertas OR e inversores dicho circuito aparece en la fig. 19 a este circuito lógico realiza la función lógica XOR.  Figura 19: Circuito lógico que realiza la función XOR

Figura 19: Circuito lógico que realiza la función XOREl símbolo lógico convencional para la puerta XOR se muestra en la fig. 20 la expresión booleana A Å B, es una expresión XOR simplificada . el símbolo Å significa la función XOR en álgebra booleana. Se dice que las entradas A y B de la fig. 20 realiza la función OR - exclusiva.

Símbolo lógico de una compuerta XOR

Símbolo lógico de una compuerta XORFAMILIAS DE PROCESADORES TTL Y CMOS

Con respecto a las familias cabe distinguir:

- TTL : Serie estándar

- TTL-L (low power) : Serie de bajo consumo

- TTL-S (schottky) : Serie rápida (usa diodos Schottky)

- TTL-AS (advanced schottky) : Versión mejorada de la serie anterior

- TTL-LS (low power schottky) : Combinación de las tecnologías L y S (es la familia más extendida)

- TTL-ALS (advanced low power schottky) : Versión mejorada de la serie LS

- TTL-F (FAST : fairchild advanced schottky)

- TTL-AF (advanced FAST) : Versión mejorada de la serie F

- TTL-HCT (high speed C-MOS) : Serie HC dotada de niveles lógicos compatibles con TTL

Características

- Su tensión de alimentación característica se halla comprendida entre los 4,75v y los 5,25V (como se ve un rango muy estrecho).

- Los niveles lógicos vienen definidos por el rango de tensión comprendida entre 0,2V y 0,8V para el estado L (bajo) y los 2,4V y Vcc para el estado H (alto).

- La velocidad de transmisión entre los estados lógicos es su mejor base, si bien esta característica le hace aumentar su consumo siendo su mayor enemigo. Motivo por el cual han aparecido diferentes versiones de TTL como FAST, LS, S, etc y últimamente los CMOS: HC, HCT y HCTLS. En algunos casos puede alcanzar poco más de los 250 MHz.

- Las señales de salida TTL se degradan rápidamente si no se transmiten a través de circuitos adicionales de transmisión (no pueden viajar más de 2 m por cable sin graves pérdidas)

Circuitos CMOS (Complementary Metal-Oxide Semiconductor)

CMOS es una de las familias lógicas empleadas en la fabricación de circuitos integrados. Su principal característica consiste en la utilización conjunta de transistores de tipo pMOS y tipo nMOS configurados de tal forma que, en estado de reposo, el consumo de energía es únicamente el debido a las corrientes parásitas.

En la actualidad, la mayoría de los circuitos integrados que se fabrican utilizan la tecnología CMOS. Esto incluye microprocesadores, memorias, procesadores digitales de señales y muchos otros tipos de circuitos integrados digitales.

* Cuando la entrada es 1, el transistor nMOS está en estado de conducción. Al estar su fuente conectada a tierra (0), el valor 0 se propaga al drenador y por lo tanto a la salida de la puerta lógica. El transistor pMOS, por el contrario, está en estado de no conducción

* Cuando la entrada es 0, el transistor pMOS está en estado de conducción. Al estar su fuente conectada a la alimentación (1), el valor 1 se propaga al drenador y por lo tanto a la salida de la puerta lógica. El transistor nMOS, por el contrario, está en estado de no conducción.

Otra de las características importantes de los circuitos CMOS es que son regenerativos: una señal degradada que acometa una puerta lógica CMOS se verá restaurada a su valor lógico inicial 0 ó 1, siempre y cuando aún esté dentro de los márgenes de ruido que el circuito pueda tolerar.

No hay comentarios:

Publicar un comentario